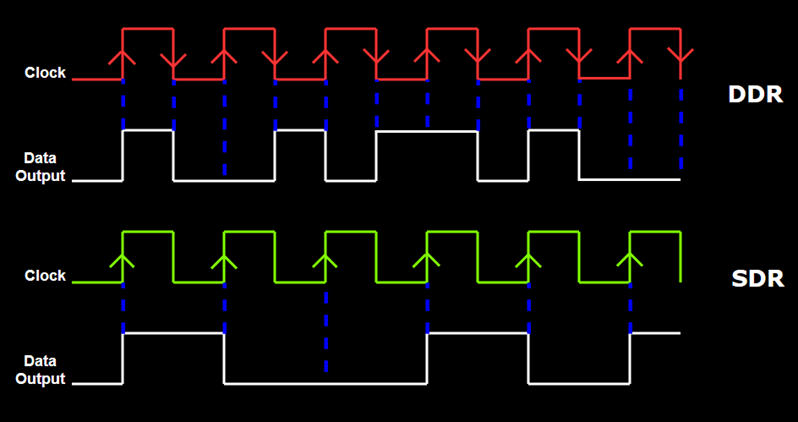

Figure 8 from A robust and low power dual data rate (DDR) flip-flop using c-elements | Semantic Scholar

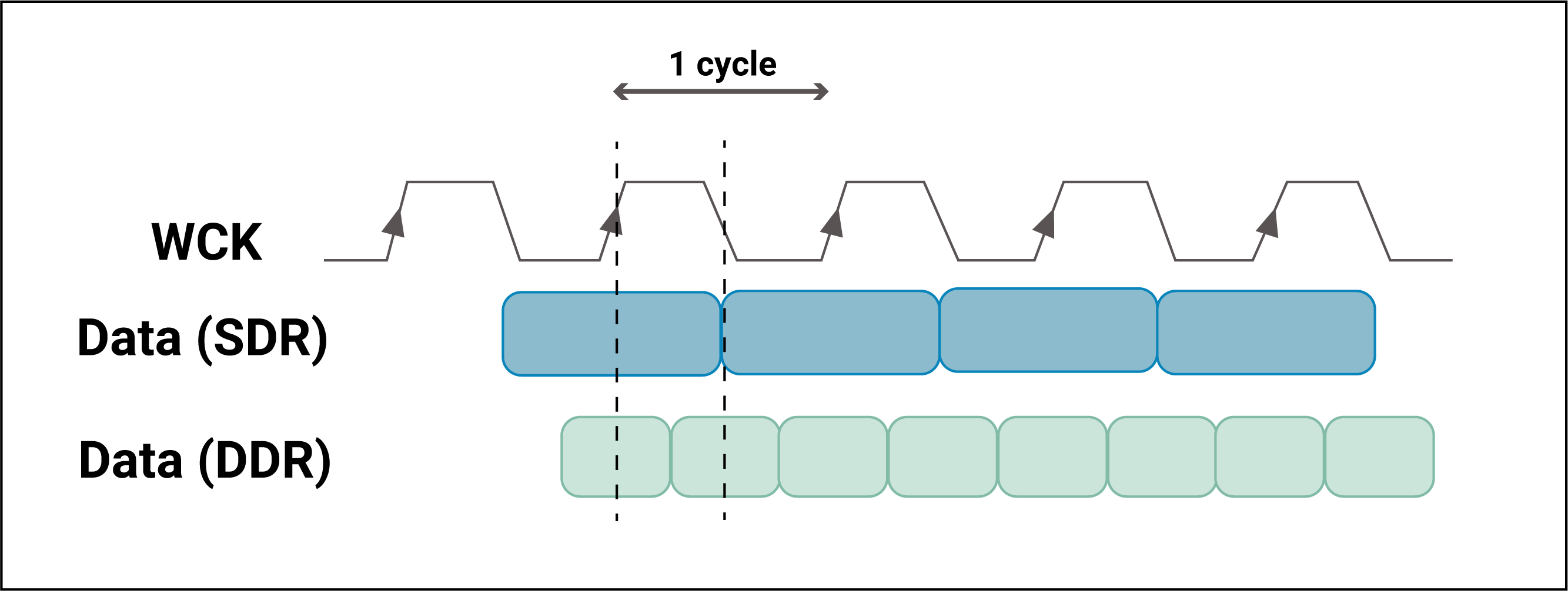

Figure 3 from A robust and low power dual data rate (DDR) flip-flop using c-elements | Semantic Scholar

Amazon.com | Havaianas Brazil Mix Flip Flops Black/White 45/46 Brazil (US Men's 12/13, Women's 14/15) M | Flip-Flops

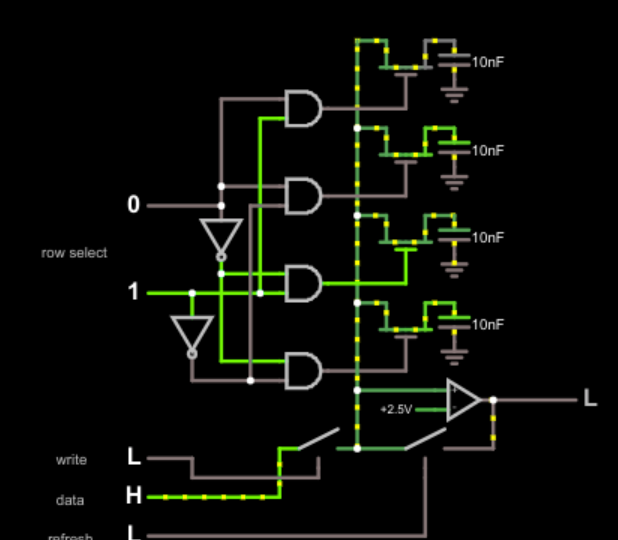

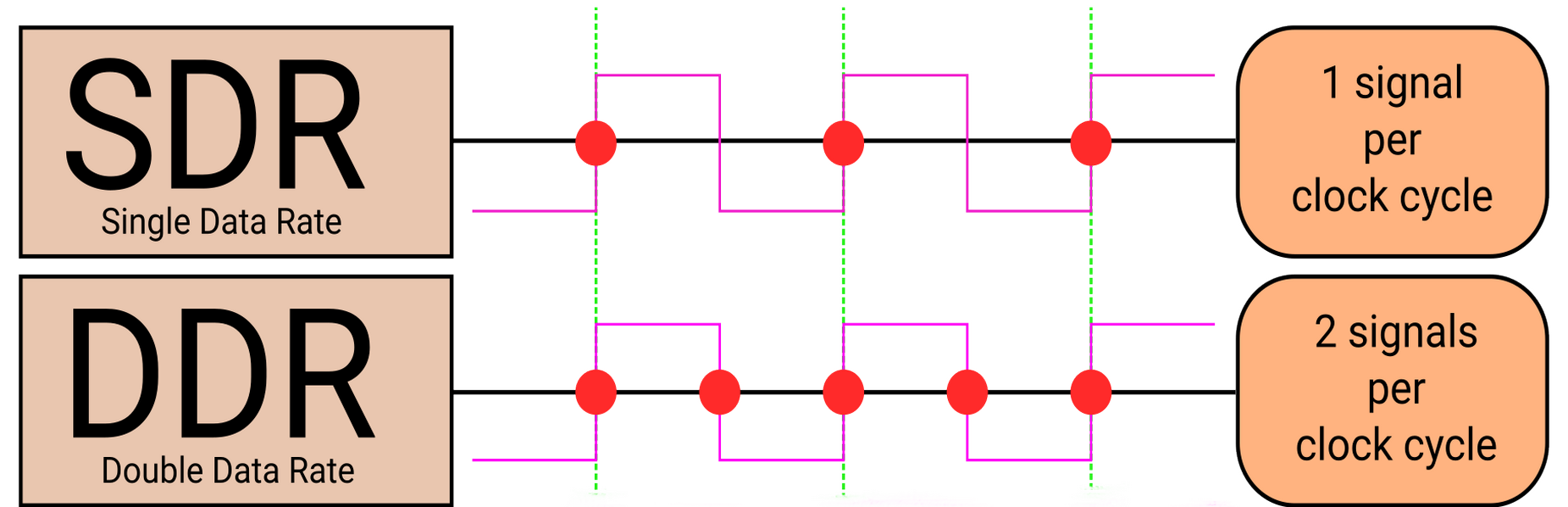

Figure 1 from A robust and low power dual data rate (DDR) flip-flop using c-elements | Semantic Scholar

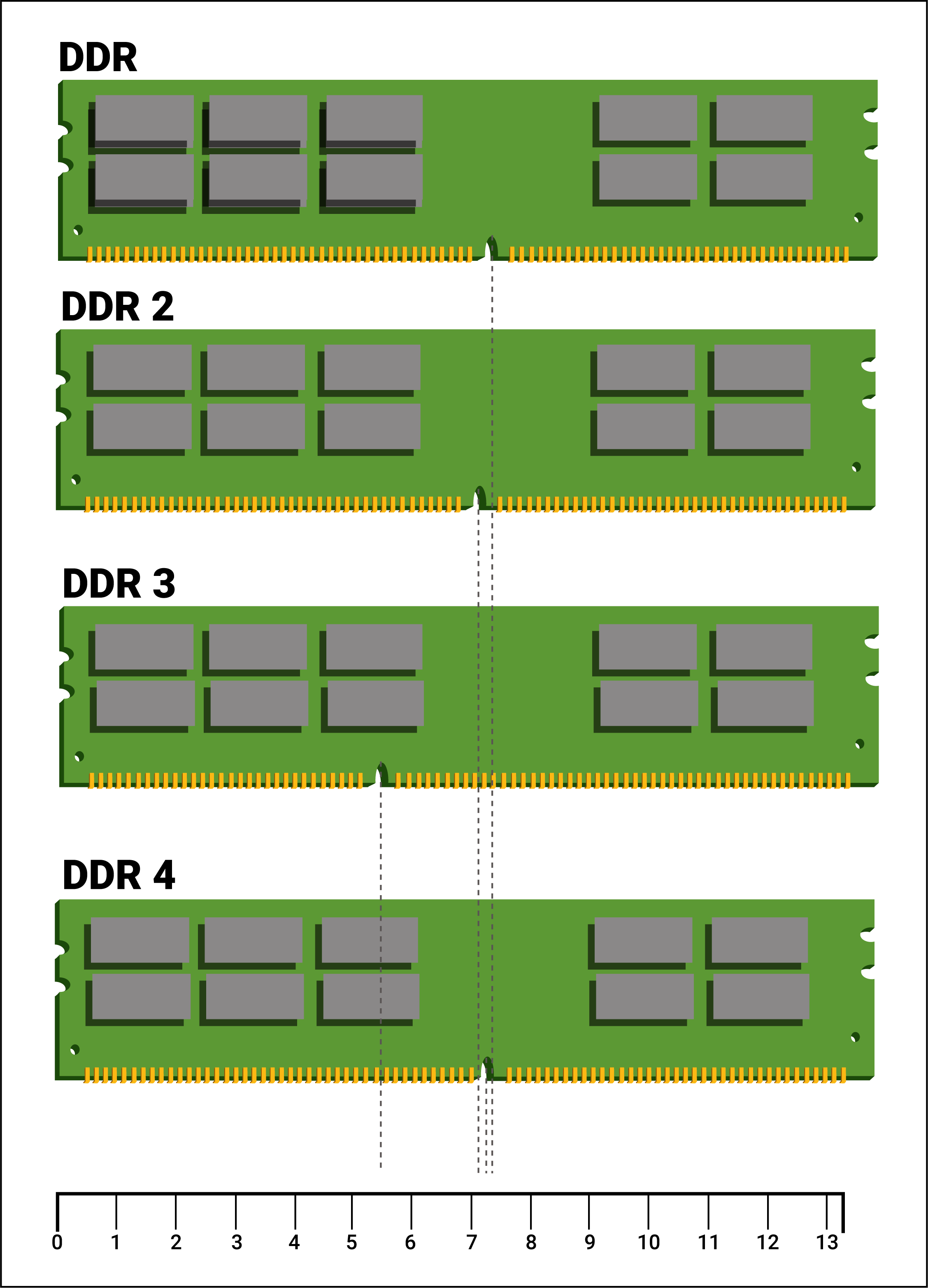

Figure 2 from A robust and low power dual data rate (DDR) flip-flop using c-elements | Semantic Scholar