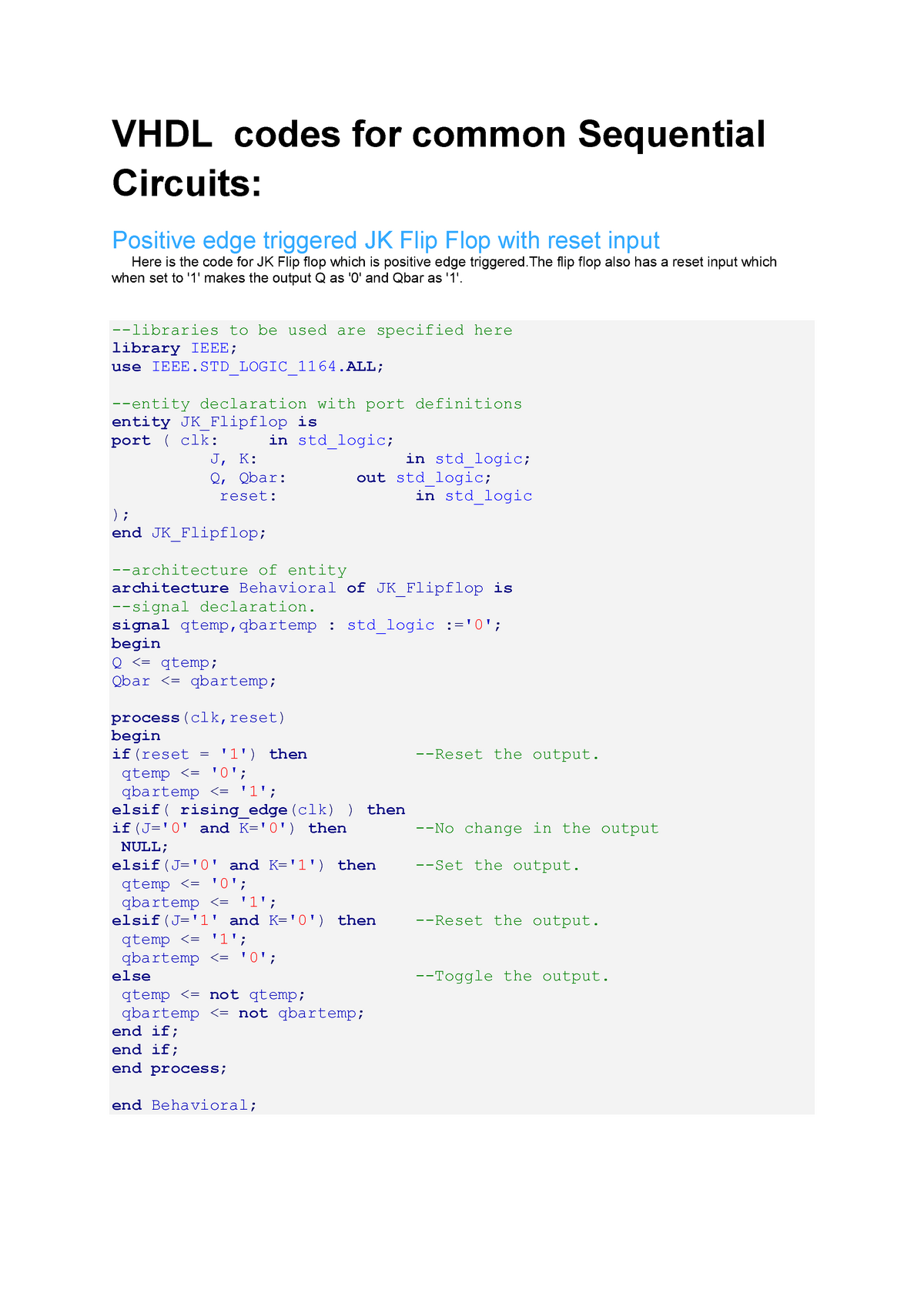

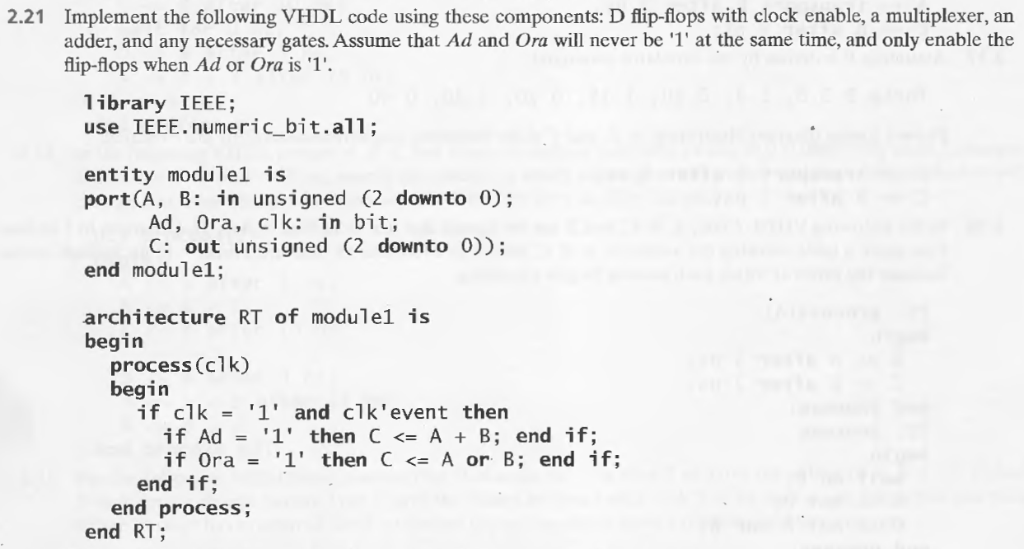

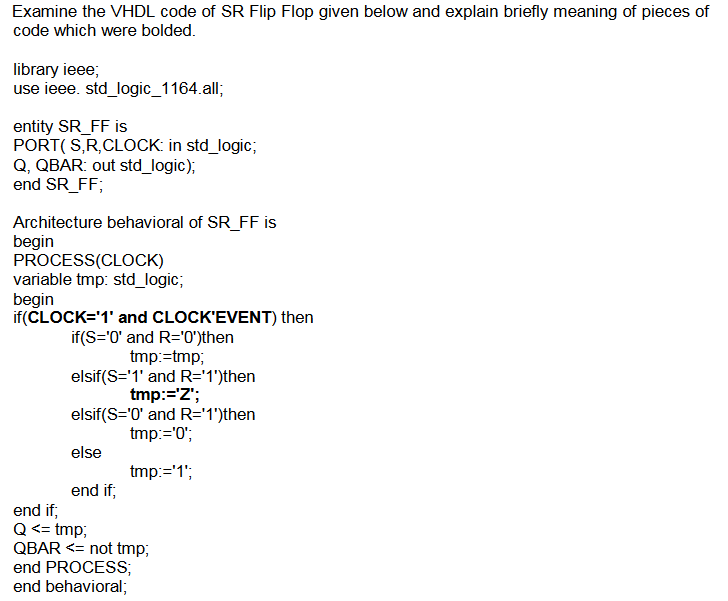

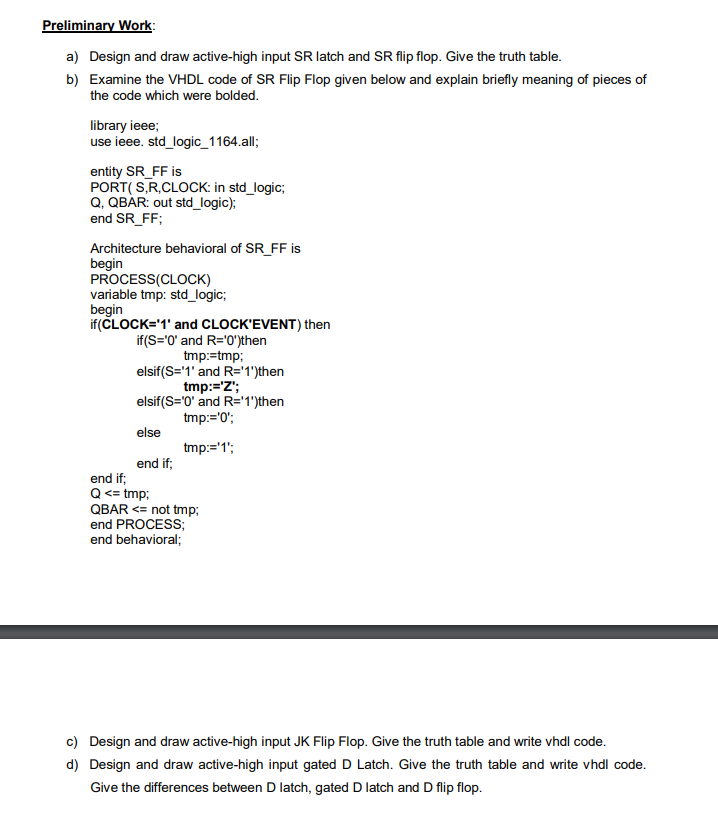

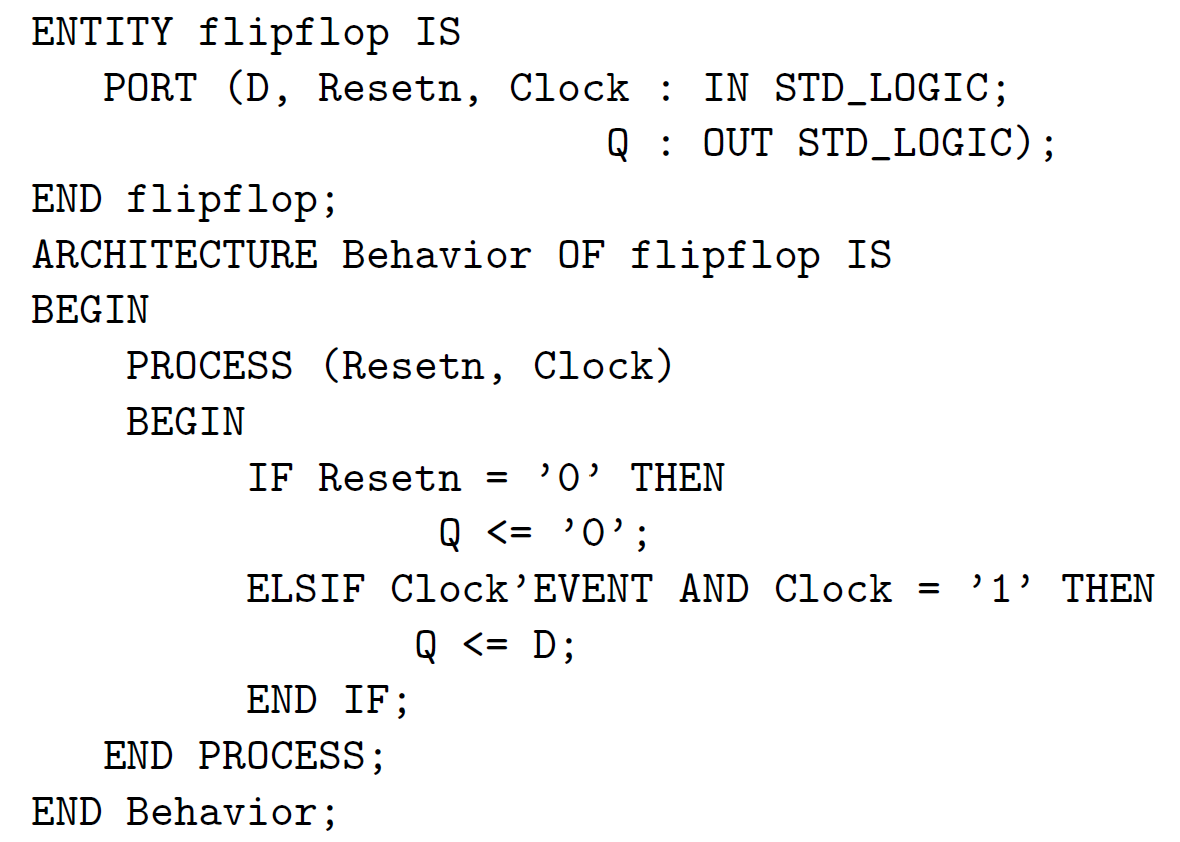

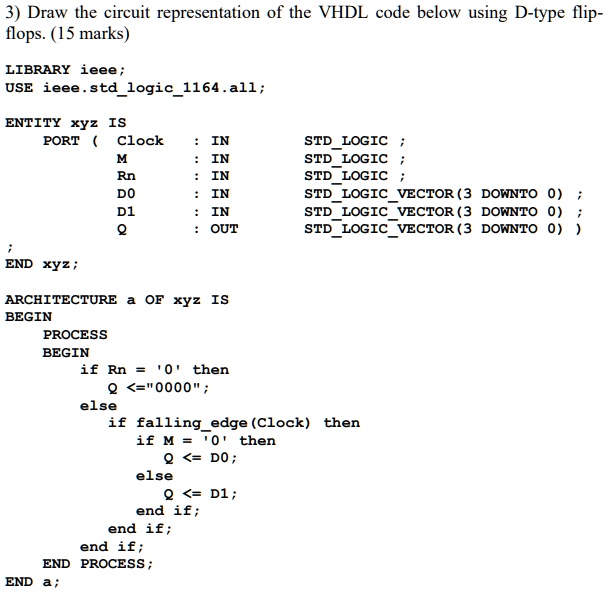

SOLVED: 3) Draw the circuit representation of the VHDL code below using D-type flip flops. (15 marks) LIBRARY ieee; USE ieee.std logicl164.all; ENTITY xyz IS PORT Clock M Rn DO D1 Q ;

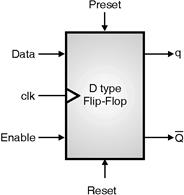

![8.5 Registers - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book] 8.5 Registers - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book]](https://www.oreilly.com/api/v2/epubs/9780470900550/files/images/ch008-f028.jpg)

8.5 Registers - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book]